Difference between revisions of "Readout Card firmware"

From MCEWiki

| (150 intermediate revisions by 5 users not shown) | |||

| Line 1: | Line 1: | ||

| − | * | + | {{Related|Readout Card Firmware}} |

| + | An overview of the firmware implemented in Readout card is described here: [[http://www.phas.ubc.ca/%7Emce/mcedocs/hardware/tech_description/SC2_ELE_S582_501_readout_card_description.pdf PDF]] | ||

| + | * Synthesis Reminders (for firmware developers) | ||

| + | ** Remember that readout_card/fsfb_clac/source/rtl/ram_40x64.vhd must be initialized with the ram_40x64.hex file in the same directory. | ||

| + | = Revision 6.0.3 = | ||

| + | * '''Filename:''' | ||

| + | ** [http://e-mode.phas.ubc.ca/mce/firmware/rc_stratix3_v06000003_20160601.sof rc_stratix3_v06000003_20160601.sof] | ||

| + | * ''' Features:''' | ||

| + | ** 6.0.2 was built based on a version that had an unsuccessful attempt to fix the filter dynamic-range issue. This version reverts back to 5.2.1 for fsfb_calc implementation. | ||

| + | * '''bugs''' | ||

| + | ** per-pixel servo reset doesn't also reset the filter | ||

| + | ** resetting any pixel with per-pixel reset also resets all the pixels in the last row (as specified by {{param|sys|num_rows}}, ignoring {{param|ac|row_order}}) | ||

| + | |||

| + | = Revision 6.0.2 (TEST!) = | ||

| + | * '''Filename:''' | ||

| + | ** [http://e-mode.phas.ubc.ca/mce/firmware/rc_stratix3_v06000002_20160509.sof rc_stratix3_v06000002_20160509.sof] | ||

| + | ** [http://e-mode.phas.ubc.ca/mce/firmware/rc_stratix3_v06000002_20160509.jic rc_stratix3_v06000002_20160509.jic] | ||

| + | |||

| + | * '''Features''' | ||

| + | **built based on 5.2.2 | ||

| + | **added support of upper 32 word needs an additional wait cycle for ack_read | ||

| + | ** delay wishbone readback by one clock cycle for reading back flx_quanta and adc_offset, | ||

| + | ** there seem to be a filter gain of factor of 2 added | ||

| + | |||

| + | * '''bugs''' | ||

| + | ** per-pixel servo reset doesn't also reset the filter | ||

| + | ** resetting any pixel with per-pixel reset also resets all the pixels in the last row (as specified by {{param|sys|num_rows}}, ignoring {{param|ac|row_order}}) | ||

| + | ** it seems to have a different filter gain | ||

| + | |||

| + | = Revision 5.2.2 (TEST!) = | ||

| + | * '''Filename:''' | ||

| + | ** [http://e-mode.phas.ubc.ca/mce/firmware/rc_stratix3_v050200002_17oct2014.sof rc_stratix3_v050200002_17oct2014.sof] | ||

| + | |||

| + | * '''bugfix or enhancement?''' | ||

| + | ** fixes a dynamic-range issue with the filter by applying a 20-bit window to the output of stage 1 filter (with lsb being configurable) before passing it on the next stage. | ||

| + | * '''bugs''' | ||

| + | ** per-pixel servo reset doesn't also reset the filter | ||

| + | ** resetting any pixel with per-pixel reset also resets all the pixels in the last row (as specified by {{param|sys|num_rows}}, ignoring {{param|ac|row_order}}) | ||

| + | |||

| + | = Revision 5.2.1 (recommended!) = | ||

| + | * '''Filename:''' | ||

| + | ** rc_stratixIII_v05020001_05jun2014.sof | ||

| + | |||

| + | * '''bugfix''' | ||

| + | ** {{param|rc|servo_rst_col0|servo_rst_col''#''}} now works for all columns! (bug reported in 5.2.0) | ||

| + | * '''bugs''' | ||

| + | ** per-pixel servo reset doesn't also reset the filter | ||

| + | ** resetting any pixel with per-pixel reset also resets all the pixels in the last row (as specified by {{param|sys|num_rows}}, ignoring {{param|ac|row_order}}) | ||

| + | |||

| + | = Revision 5.2.0 = | ||

| + | * '''Filename:''' | ||

| + | ** rc_stratixIII_v05020000_28may2013.sof | ||

| + | |||

| + | * '''Features:''' | ||

| + | ** added the ability to reset the flux-loop servo on per-detector basis by adding {{param|rc|servo_rst_arm}} and {{param|rc|servo_rst_col0|servo_rst_col''#''}} parameters. This will reset the integral_term, the integral_clamp, anf flux-jump counter. | ||

| + | |||

| + | * '''bug:''' | ||

| + | ** {{param|rc|servo_rst_col0|servo_rst_col''#''}} works for col 0 and 1, but not for col2 to 7! This is fixed in 5.2.1 | ||

| + | ** per-pixel servo reset doesn't also reset the filter | ||

| + | ** resetting any pixel with per-pixel reset also resets all the pixels in the last row (as specified by {{param|sys|num_rows}}, ignoring {{param|ac|row_order}}) | ||

| + | |||

| + | = Revision 5.1.d = | ||

| + | * '''Filename:''' | ||

| + | ** rc_stratixIII_v0501000d_30oct2012.sof | ||

| + | |||

| + | * '''Features:''' | ||

| + | ** flux-jump routine is revamped to minimize the additional delay for applying sq1fb when flux-jump is enabled. In this version sq1fb DAC is refreshed at clock cycle 10 of each row visit when flux-jump is enabled and at clock cycle 7 when flux-jump is disabled. | ||

| + | ** extended dynamic range of the filter by increasing the width of filter-delay terms from 29 to 32 bits | ||

| + | ** lower power consumption (maybe?) | ||

| + | |||

| + | * '''Details''' | ||

| + | ** DDR2 module not instantiated (chips not installed) and on-chip termination resistors not in effect which can potentially save power. | ||

| + | |||

| + | === Revision 5.1.c (Test) === | ||

| + | * '''Filename:''' | ||

| + | ** rc_stratixIII_v0501000c_31aug2012.sof | ||

| + | |||

| + | * '''Features:''' | ||

| + | ** extended dynamic range of the filter by increasing the width of filter-delay terms from 29 to 32 bits | ||

| + | ** based on 5.1.a | ||

| + | ** lower power consumption (maybe?) | ||

| + | ** {{param|rc|data_mode}}=4 reports fb(29 downto 12) instead of fb(31) & fb(28 downto 12)! no sticky bit. | ||

| + | |||

| + | * '''Details''' | ||

| + | ** DDR2 module not instantiated (chips not installed) and on-chip termination resistors not in effect which can potentially save power. | ||

| + | |||

| + | = Revision 5.1.b (Stable '''Rev.B''' Cards) = | ||

| + | * '''Filename:''' | ||

| + | ** rc_v0501000b_23mar2012.sof (Rev. B cards) | ||

| + | |||

| + | * '''Features:''' | ||

| + | ** based on 5.1.8 (used Q11SP1) | ||

| + | ** added intergral_term fix from 5.1.9 | ||

| + | |||

| + | * '''Details''' | ||

| + | ** qterm (or filtered-p) implementation is not included, because the design doesn't fit on the FPGA on Rev. B cards anymore. | ||

| + | |||

| + | = Revision 5.1.a (Stable) = | ||

| + | * '''Filename:''' | ||

| + | ** rc_stratix3_v0501000a_24jan2012.sof (Rev. E cards) | ||

| + | |||

| + | * '''Features:''' | ||

| + | ** based on 5.1.9 (used Q10SP1) | ||

| + | ** {{param|rc|pterm_decay_bits}} (par_id = 0x64) is now '''programmable''' and is initially set to 0 to have pure p-term and be compatible with older firmware. (p-term implemented as q(n) = er(n) + b*q(n-1) where b=(1-1/2^k)with k={{param|rc|pterm_decay_bits}}) | ||

| + | ** see bugfix in 5.1.9 | ||

| + | |||

| + | == Revision 5.1.9 (test) == | ||

| + | * '''Filename:''' | ||

| + | ** rc_stratix3_v05010009_23jan2012.sof (for Rev. E cards) | ||

| + | |||

| + | * '''Features:''' | ||

| + | ** based on 5.1.8 (used Q10SP1) | ||

| + | ** first implementation of decayed-p-term in sq1fb calculation. The p-term is now implemented as q(n) = er(n) + b*q(n-1) where b=(1-1/2^k) and '''k=3 hardcoded'''. | ||

| + | ** added {{param|rc|pterm_decay_bits}} (par_id=0x64) as a register set to 3, but not tied to k in pterm calculation yet. | ||

| + | |||

| + | * ''' Bugfix:''' | ||

| + | ** This version fixes the bug introduced starting 5.0.e, the integral-term used to calculate sq1fb was calculated based on coadded value of (sample_num-1) samples and then the integral term stored for next round included sample_num-2. This is almost like having a p-term.. | ||

| + | |||

| + | == Revision 5.1.8 (s1fb_dly=7) == | ||

| + | * '''Filename:''' | ||

| + | ** rc_stratix3_v05010008_11jan2012.sof (for Rev. E cards) | ||

| + | |||

| + | * '''Features:''' | ||

| + | ** based on 5.1.7 (used Q10SP1) | ||

| + | ** reverts back to applying S1fb after 7 clock cycles when flux-jump is off, and after 18 clock cycles when flux-jump is on. | ||

| + | |||

| + | == Revision 5.1.7 (rectangle-mode bugfix) == | ||

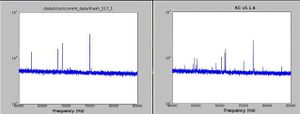

| + | [[File:RC516 vs RC517 hash.jpeg|thumb|Reduction in high-frequency noise due to rectangle-mode bugfix]] | ||

| + | * '''Filename:''' | ||

| + | ** rc_stratix3_v05010007_17nov2011.sof (for Rev. E cards) | ||

| + | |||

| + | * '''Features:''' | ||

| + | ** based on 5.1.6 (used Q10SP1) | ||

| + | |||

| + | * ''' Bugfix:''' | ||

| + | ** In all RC firmware prior to 5.1.7, the read pointer in the rectangle-mode data was being refreshed at ARZ even if it was in the middle of a long readout (large frame readout). This resulted in seeing '''duplicate data in high-data-rate rectangle-mode readout''' only when the following condition was _NOT_ true: (230 + 2*{{param|cc|num_rows_reported|cc num_rows_reported}}*{{param|cc|num_cols_reported|cc num_cols_reported}}) < ({{param|sys|num_rows}}*{{param|sys|row_len}}). This is fixed in 5.1.7. | ||

| + | |||

| + | = Revision 5.1.6 (Stable) = | ||

| + | * '''Filename:''' | ||

| + | ** rc_stratix3_v05010006_27oct2011.sof (for Rev. E cards) | ||

| − | * | + | * '''Features:''' |

| − | ** | + | ** based on 5.1.5 (used Q10SP1) |

| − | ** | + | ** coadd window and feedback-calculation blocks are adjusted for ADC latency of readout card Rev. E |

| + | |||

| + | * ''' Bugfix:''' | ||

| + | ** {{param|rc|sample_dly}} + {{param|rc|sample_num}} = {{param|sys|row_len}} should work now. | ||

| + | |||

| + | == Revision 5.1.5 (test)== | ||

| + | * '''Filename:''' | ||

| + | ** rc_stratix3_v05010005_15sep2011.sof (for Rev. E cards) | ||

| + | |||

| + | * '''Features:''' | ||

| + | ** based on 5.1.2 | ||

| + | ** reverts back to applying SQ1FB after 18 clock cycles whether flux-jumping is on or off | ||

| + | |||

| + | * ''' Bugfix:''' | ||

| + | ** All stratixiii firmware revisions prior to this version adjusted the co-add window for an ADC latency of 4 instead of 11. (Rev. E RC has serial ADC installed with 11 clock cycle latency.) The coadd window is now adjusted properly. | ||

| + | |||

| + | *'''Bug:''' | ||

| + | ** The last row samples can not be used in {{param|rc|servo_mode}}=3. For proper operation: {{param|rc|sample_dly}} + {{param|rc|sample_num}} needs to be < {{param|sys|row_len}} - 7 (I think). Although, the coadd window was adjusted in this version, but the calculation block latches data before coadd is done (coadd_done_o signal). | ||

| + | |||

| + | == Revision 5.1.4 (Scuba2) == | ||

| + | |||

| + | * '''Filename:''' | ||

| + | ** rc_v05010004_01jun2011.sof (for Rev. B cards) | ||

| + | |||

| + | * '''Features:''' | ||

| + | ** based on 5.1.3 | ||

| + | ** sq1_fb applied after 7 clock cycles when flux-jump off, and after 18 when flux-jump is on. | ||

| + | * ''' bugfix:''' | ||

| + | ** fixed bug with fsfb_corr when reverting back to applying sq1fb after 7 clk cycles when fj is off | ||

| + | |||

| + | == Revision 5.1.3 (Scuba2) == | ||

| + | * '''Filename:''' | ||

| + | ** rc_v05010003_01jun2011.sof (for Rev. B cards) | ||

| + | |||

| + | * '''Features:''' | ||

| + | ** based on 5.1.2 | ||

| + | ** reverts back to applying SQ1FB after 7 clock cyclces when flux-jumping is off, and after 18 clock cycles when flux-jumping is on. | ||

| + | ** k1 of filter params is now limited to k1<8. After generating coeffs for many filters, it is certain that this range is more than what we ever need. | ||

| + | |||

| + | = Revision 5.1.2 (Stable)= | ||

| + | * '''Filename:''' | ||

| + | ** rc_stratix3_v05010002_18jan2011.sof (for Rev. E cards) | ||

| + | ** rc_stratix3_v05010002_18jan2011.jic (for Rev. E cards) | ||

| + | ** rc_v05010002_03feb2011.sof (for Rev. B cards) | ||

| + | ** rc_v05010002_03feb2011.pof (for Rev. B cards) | ||

| + | |||

| + | * '''Features:''' | ||

| + | ** based on 5.1.1 with k1 and k2 (filter params) limited to k1<16 and k2<32 in order to resolve the timing when compiling for smaller Stratix FPGA on RC Rev. B. | ||

| + | |||

| + | * '''Bug fix:''' | ||

| + | ** the 2-rows-off filtered data readout introduced with configurable filter in rev. 5.1.0 and 5.1.1 is fixed now. | ||

| + | |||

| + | * '''Bugs:''' | ||

| + | ** none so far. | ||

| + | |||

| + | * '''FPGA Resource Usage''' (readout_card.fit.rpt, rev. B) | ||

| + | ; Total logic elements ; 33,285 / 41,250 ( 81 % ) ; | ||

| + | ; Total pins ; 358 / 616 ( 58 % ) ; | ||

| + | ; Total memory bits ; 1,405,440 / 3,423,744 ( 41 % ) ; | ||

| + | |||

| + | * '''FPGA Timing Analysis''' (readout_card.tan.rpt, rev. B) | ||

| + | ; Fast Model Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk2' ; 6.591 ns | ||

| + | ; Fast Model Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk0' ; 7.206 ns | ||

| + | ; Fast Model Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk3' ; 18.299 ns | ||

| + | |||

| + | == Revision 5.1.1 (test only) == | ||

| + | * '''Filename:''' | ||

| + | ** rc_v05010001_01dec2010.sof (for Rev. B cards) | ||

| + | |||

| + | * '''Features:''' | ||

| + | ** based on 5.1.0, but k1 and k2 (filter params) are now limited to k1<16 and k2<32 in order to resolve the timing failures of compiling 5.1.0 for smaller Stratix FPGA on RC Rev. B. | ||

| + | |||

| + | * '''Bugs:''' | ||

| + | ** filter mode data is off by 2 rows. | ||

| + | |||

| + | == Revision 5.1.0 (test only) == | ||

| + | * '''Filename:''' | ||

| + | ** rc_stratix3_v05010000_01nov2010.sof (for Rev. E cards) | ||

| + | ** rc_v05010000_01nov2010.sof (for Rev. B cards) has timing failures '''do not use!!!''' | ||

| + | |||

| + | * '''Features:''' | ||

| + | ** added configurable filter parameters specified by {{param|rc|fltr_coeff}}, default is the f<sub>cutoff</sub>/f<sub>sampl</sub>=122Hz/15kHz. see [[ Digital 4-pole Butterworth Low-pass filter ]]. | ||

| + | ** {{param|rc|fltr_type}} is set to 255 to indicate configurable filter parameters. | ||

| + | * '''Details''' | ||

| + | ** It is built on Quartus10.1. | ||

| + | ** tcl files had to be updated as cmp syntax is not supported in Q10 anymore. | ||

| + | ** Rev. E cards now can be identified by reading back pcb_rev as part of card_type, therefore both stratix I and III sof/pof/jic are generated from the same source. | ||

| + | |||

| + | * '''Bugs:''' | ||

| + | ** rc_v05010000_01nov2010.sof has timing failures that were overlooked, do not use this firmware for Rev.B cards. | ||

| + | ** '''filter mode data is off by 2 rows.''' | ||

| + | |||

| + | * '''FPGA Resource Usage and Timing Report''' (readout_card.fit.rpt and readout_card.tan.rpt): logic usage is upto 85% from 66% in 5.0.d/e/f | ||

| + | |||

| + | = Revision 5.0.f (Stable) = | ||

| + | * '''Filename:''' | ||

| + | ** rc_v0500000f_22oct2010.sof (for Rev. B cards) | ||

| + | ** rc_stratix3_v0500000f_22oct2010.sof (for Rev. E cards) | ||

| + | |||

| + | * '''Features:''' | ||

| + | ** Bugfix: integral clamp should work now. only positive integral_clamp values are valid! | ||

| + | |||

| + | * '''Details:''': | ||

| + | ** SQ1FB is applied 18 clock cycles after start of a row visit (SQ1_Bias being applied) regardless of flux-jump being enabled or not. In pre-5.0.b firmware SQ1FB was being applied after 7 clock cycles when flux-jump was disabled and after 18 clock cycles when flux-jump was enabled. | ||

| + | ** available for both Rev. E and Rev. B cards, the upper byte of card_type parameter now reports the pcb revision. | ||

| + | ** development note: It is built on Quartus10.1. | ||

| + | |||

| + | * '''Bugs:''' | ||

| + | **none yet! | ||

| + | |||

| + | * '''FPGA Resource Usage''' (readout_card.fit.rpt): | ||

| + | ; Total logic elements ; 27,377 / 41,250 ( 66 % ) ; | ||

| + | ; Total pins ; 358 / 616 ( 58 % ) ; | ||

| + | ; Total memory bits ; 1,405,440 / 3,423,744 ( 41 % ) ; | ||

| + | |||

| + | * '''FPGA Timing Analysis''' (readout_card.tan.rpt): | ||

| + | ; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk0' ; 2.652 ns | ||

| + | ; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk2' ; 3.385 ns | ||

| + | ; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk3' ; 16.860 ns | ||

| + | |||

| + | == Revision 5.0.e (test only) == | ||

| + | * '''Filename:''' | ||

| + | ** rc_v0500000e_06oct2010.sof | ||

| + | |||

| + | * '''Details:''' | ||

| + | ** an unsuccessful attempt to fix {{param|rc|integral_clamp}}, but changed the functionality so that it clamps at the value, but it doesn't hold the clamp. i.e., if the calculated sq1fb becomes less than the specified clamp value, the sq1fb is not clamped anymore. This is not a desired functionality! | ||

| + | |||

| + | == Revision 5.0.d (test only) == | ||

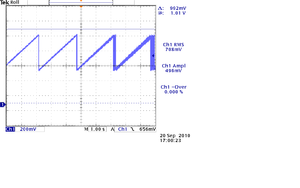

| + | [[Image:Clamp_unstable.png|thumb|right|Scope snapshot]] | ||

| + | * '''Filename:''' | ||

| + | ** rc_v0500000d_04aug2010.sof | ||

| + | |||

| + | * '''Features:''' | ||

| + | ** Bugfix: To fix the bug associated with negative flux-jumps, reverted to signed multiplier and hence, incremented the width of the flux-quanta multiplier input by 1. | ||

| + | |||

| + | * '''Details:''': | ||

| + | ** SQ1FB is applied 18 clock cycles after start of a row visit (SQ1_Bias being applied) regardless of flux-jump being enabled or not. In pre-5.0.b firmware SQ1FB was being applied after 7 clock cycles when flux-jump was disabled and after 18 clock cycles when flux-jump was enabled. | ||

| + | |||

| + | * '''Bugs:''' | ||

| + | ** '''{{param|rc|integral_clamp}} is broken'''. To test the clamping, a servo-locked ramp was initiated on the sq1fb and then flux-jumping was turned on and observed by attaching a scope to the SQ1FB output. With {{param|rc|integral_clamp}}=80000000, {{param|rc|flx_quanta0|flux_quanta}}=8000, {{param|rc|gaini0|gaini}}=1, flux-jump enabled, we see scope snapshot used slow_fb_ramp.py script for testing. | ||

| + | |||

| + | * '''FPGA Resource Usage and Timing Report''' (readout_card.fit.rpt and readout_card.tan.rpt): no change compared to 5.0.a/b/c | ||

| + | |||

| + | == Revision 5.0.c (test only) == | ||

| + | * '''Filename:''' | ||

| + | ** rc_v0500000c_16jun2010.sof | ||

| + | |||

| + | * '''Features:''' | ||

| + | ** Based on rev. 5.0.b | ||

| + | ** Re-introduced flux-jump counter clamping to maintain continuity in behavior from past versions of firmware in the field. | ||

| + | ** '''Important''': SQ1FB is applied 18 clock cycles after start of a row visit (SQ1_Bias being applied) regardless of flux-jump being enabled or not. In pre-5.0.b firmware SQ1FB was being applied after 7 clock cycles when flux-jump was disabled and after 18 clock cycles when flux-jump was enabled. | ||

| + | |||

| + | * '''Details:''' | ||

| + | * '''Bugs:''' | ||

| + | ** '''flux-jump is broken'''. flux-jumping block misbehaves at the first jump in the negative range. | ||

| + | |||

| + | * '''FPGA Resource Usage''' (readout_card.fit.rpt): | ||

| + | ; Total logic elements ; 26,800 / 41,250 ( 65 % ) ; | ||

| + | ; Total pins ; 358 / 616 ( 58 % ) ; | ||

| + | ; Total virtual pins ; 0 ; | ||

| + | ; Total memory bits ; 1,405,440 / 3,423,744 ( 41 % ) ; | ||

| + | ; DSP block 9-bit elements ; 76 / 112 ( 68 % ) ; | ||

| + | ; Total PLLs ; 1 / 6 ( 17 % ) ; | ||

| + | ; Total DLLs ; 0 / 2 ( 0 % ) ; | ||

| + | |||

| + | * '''FPGA Timing Analysis''' (readout_card.tan.rpt): | ||

| + | ; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk0' ; 1.964 ns ; | ||

| + | ; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk2' ; 4.382 ns ; | ||

| + | ; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk3' ; 15.924 ns ; | ||

| − | + | == Revision 5.0.b (test only) == | |

| − | == Revision 5.0. | ||

* '''Filename:''' | * '''Filename:''' | ||

** rc_v0500000b_03jun2010.sof | ** rc_v0500000b_03jun2010.sof | ||

* '''Features:''' | * '''Features:''' | ||

| − | ** Based on rev. 5.0. | + | ** Based on rev. 5.0.a |

| − | ** | + | ** A bug that caused jumps in first-stage feedback, and detected as spikes in the raw data of pixels that were in servo_mode=0,1,2 was fixed. The jumps in FSFB were due to flux-jumping being enabled on live pixels with non-zero {{param|rc|flx_quanta0|flx_quanta}}, and being disabled on the fly on dead pixels with {{param|rc|flx_quanta0|flx_quanta}}=0. Flux-jumping is now disabled on a column-by-column basis if a column is in servo_mode = 0,1,2. |

| − | ** Ineffective clamping was | + | ** Ineffective clamping was removed from the flux-jumping block (as per 5.0.9), as it is now replaced by the clamping that was perfected in rev. 5.0.10 |

| − | ** A sticky bit was also removed from the flux-jumping block. | + | ** A sticky bit that only affected servo_mode=0,1,2 was also removed from the flux-jumping block. |

| − | ** The code was re-arranged in the flux-jumping block to reflect the flow of data through the pipeline and make it easier to understand. | + | ** {{param|rc|flx_lp_init}} commands now also clear the flux-jumping block as well. |

| + | ** The 11-clock-cycle delay (in applying SQ1_FB) that in previous firmware only occurred when flux-jumping was enabled, now (in this version) is in effect all the time. Due to the bug-fix above, flux-jumping can be disabled on a column-by-column basis by setting servo_mode=0,1,2 when {{param|rc|en_fb_jump}}=1. Before the change, this meant that constant values could be applied with or without the 11-cycle delay if {{param|rc|en_fb_jump}}=1 or 0. To make the delay consistent, it is now always 11 cycles. As background, the flux-jumping block is pipelined, meaning that it does calculations for all 8 channels serially. The serialization is because of DSP-block limitations in the Readout Card FPGA that prevent us from doing all 8 channels in parallel. The reason that it takes 11 cycles to complete the flux-jumping calculations is because the values are computed for the eight channels in three ALU stages: 8 + 3 = 11 cycles. Adding 11 cycles to the 7 cycles of latency from other stages in the system results in: 11 + 7 = 18 cycles of latency from the start of a row dwell period before the first-stage feedback is applied. In rc_v5.0.c, I enforce the 18-cycle delay even when flux-jumping is not enabled to maintain uniformity across all eight channels, because flux-jumping is enabled/disabled on a per-channel basis. In other words, if I hadn't enforced the 18-cycle delay, some channels could have their feedback applied after 7 cycles, while others could have it applied after 18 cycles. I wasn't a fan of this non-uniformity. I realize that 18 cycles is a long time. In fact, so is 7. In the last few months, we have been discussing how to reduce these times to 1 cycle, because every experiment out there wants to multiplex as fast as possible, and the 7/18-delay is a rate limiting step. | ||

| + | ** The flux-jumping code was re-arranged in the flux-jumping block to reflect the flow of data through the pipeline and make it easier to understand. | ||

* '''Details:''' | * '''Details:''' | ||

* '''Bugs:''' | * '''Bugs:''' | ||

| − | + | ** flux-jump does not work when jumping to negative values. | |

| − | * | ||

| − | * | ||

* '''FPGA Resource Usage''' (readout_card.fit.rpt): | * '''FPGA Resource Usage''' (readout_card.fit.rpt): | ||

| Line 32: | Line 338: | ||

; Total PLLs ; 1 / 6 ( 17 % ) ; | ; Total PLLs ; 1 / 6 ( 17 % ) ; | ||

; Total DLLs ; 0 / 2 ( 0 % ) ; | ; Total DLLs ; 0 / 2 ( 0 % ) ; | ||

| − | |||

* '''FPGA Timing Analysis''' (readout_card.tan.rpt): | * '''FPGA Timing Analysis''' (readout_card.tan.rpt): | ||

; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk0' ; 1.459 ns | ; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk0' ; 1.459 ns | ||

| Line 38: | Line 343: | ||

; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk3' ; 15.956 ns | ; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk3' ; 15.956 ns | ||

| − | == Revision 5.0. | + | == Revision 5.0.a (test only) == |

* '''Filename:''' | * '''Filename:''' | ||

** rc_v0500000a_12mar2010.sof | ** rc_v0500000a_12mar2010.sof | ||

| Line 44: | Line 349: | ||

* '''Features:''' | * '''Features:''' | ||

** Based on the merger of rev. 5.0.8 and 5.0.9. | ** Based on the merger of rev. 5.0.8 and 5.0.9. | ||

| − | ** integral_clamp command is added where a clamp value is set for the integral term and once the integral term hits that value, the integral-term is clamped to that value and p-term and d-term are clamped to zero. When integral_term=0 then no clamping is in effect, similar to previous releases of firmware. | + | ** {{param|rc|integral_clamp}} command is added where a clamp value is set for the integral term and once the integral term hits that value, the integral-term is clamped to that value and p-term and d-term are clamped to zero. When integral_term=0 then no clamping is in effect, similar to previous releases of firmware. |

** The low pass filter has 20-bit input and f_3dB/f_samp = 122Hz/15kHz . | ** The low pass filter has 20-bit input and f_3dB/f_samp = 122Hz/15kHz . | ||

** The flux-jump clamping that was removed in 5.0.9 is included once again here, as we decided this is safer for now. | ** The flux-jump clamping that was removed in 5.0.9 is included once again here, as we decided this is safer for now. | ||

* '''Details:''' | * '''Details:''' | ||

| − | ** | + | ** "lock_dat_left" parameter that was removed in 5.0.9 is now implemented as "lock_dat_lsb" |

* '''Bugs:''' | * '''Bugs:''' | ||

| + | ** {{param|rc|flx_lp_init}} does not reinitialize the flux-jump block | ||

* '''Synthesis Notes:''' | * '''Synthesis Notes:''' | ||

| Line 76: | Line 382: | ||

* '''Bugs:''' | * '''Bugs:''' | ||

| − | ** integral_clamp read/write command does not work. | + | ** {{param|rc|integral_clamp}} read/write command does not work. |

* '''Synthesis Notes:''' | * '''Synthesis Notes:''' | ||

| Line 83: | Line 389: | ||

* '''FPGA Resource Usage''' (readout_card.fit.rpt): | * '''FPGA Resource Usage''' (readout_card.fit.rpt): | ||

; Total logic elements ; 27,960 / 41,250 ( 68 % ) ; | ; Total logic elements ; 27,960 / 41,250 ( 68 % ) ; | ||

| − | |||

| − | |||

; Total memory bits ; 1,405,440 / 3,423,744 ( 41 % ) ; | ; Total memory bits ; 1,405,440 / 3,423,744 ( 41 % ) ; | ||

| − | |||

| − | |||

| − | |||

* '''FPGA Timing Analysis''' (readout_card.tan.rpt): | * '''FPGA Timing Analysis''' (readout_card.tan.rpt): | ||

| Line 100: | Line 401: | ||

* '''Features:''' | * '''Features:''' | ||

| − | ** Based on rev. 5.0.4 | + | ** Based on rev. 5.0.4 |

** type 1 low-pass filter: f<sub>3dB</sub>=122Hz for f<sub>sample</sub>=15kHz | ** type 1 low-pass filter: f<sub>3dB</sub>=122Hz for f<sub>sample</sub>=15kHz | ||

** Filter-input-width changed from 18b to 20b with no sticky bits! | ** Filter-input-width changed from 18b to 20b with no sticky bits! | ||

** removed sticky bits in internal arithmetic of the filter. | ** removed sticky bits in internal arithmetic of the filter. | ||

| − | + | = Revision 5.0.7 (type-2 filter) = | |

* '''Filename:''' | * '''Filename:''' | ||

** rc_v05000007_09oct2009.sof | ** rc_v05000007_09oct2009.sof | ||

| Line 126: | Line 427: | ||

* '''FPGA Resource Usage''' (readout_card.fit.rpt): | * '''FPGA Resource Usage''' (readout_card.fit.rpt): | ||

* '''FPGA Timing Analysis''' (readout_card.tan.rpt): | * '''FPGA Timing Analysis''' (readout_card.tan.rpt): | ||

| + | == Revision 5.0.6 (UBC only) == | ||

| + | * '''Filename:''' | ||

| + | ** rc_stratix3_v05000006_15sep2009.sof | ||

| + | |||

| + | * '''Features:''' | ||

| + | ** Only Valid for Rev. C/D Cards | ||

| + | ** Based on rev. 5.0.3 | ||

| + | ** tcl file updated for Rev. D and aligned with top-level and qsf (project file). | ||

| + | ** flux loop commented, just to try sampling the ADC. | ||

| + | ** compiled with Q9.1 | ||

== Revision 5.0.5 (UBC only) == | == Revision 5.0.5 (UBC only) == | ||

| Line 144: | Line 455: | ||

* '''FPGA Timing Analysis''' (readout_card.tan.rpt): | * '''FPGA Timing Analysis''' (readout_card.tan.rpt): | ||

| − | + | = Revision 5.0.4 (Stable) = | |

* '''Filename:''' | * '''Filename:''' | ||

** rc_v05000004_28aug2009.sof | ** rc_v05000004_28aug2009.sof | ||

| Line 164: | Line 475: | ||

* '''FPGA Resource Usage''' (readout_card.fit.rpt): | * '''FPGA Resource Usage''' (readout_card.fit.rpt): | ||

; Total logic elements ; 26,170 / 41,250 ( 63 % ) ; | ; Total logic elements ; 26,170 / 41,250 ( 63 % ) ; | ||

| − | |||

| − | |||

; Total memory bits ; 1,405,440 / 3,423,744 ( 41 % ) ; | ; Total memory bits ; 1,405,440 / 3,423,744 ( 41 % ) ; | ||

| − | |||

| − | |||

| − | |||

* '''FPGA Timing Analysis''' (readout_card.tan.rpt): | * '''FPGA Timing Analysis''' (readout_card.tan.rpt): | ||

| Line 176: | Line 482: | ||

; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk3' ; 15.398 ns ; | ; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk3' ; 15.398 ns ; | ||

| − | == Revision 5.0.2 ( | + | = Revision 5.0.3 = |

| + | * '''Filename:''' | ||

| + | ** rc_stratix3_v05000003_21aug2009.sof | ||

| + | |||

| + | * '''Features:''' | ||

| + | ** ONLY valid REV C/D RC Cards | ||

| + | ** Based on rev. 5.0.2 | ||

| + | ** flux loop commented, just to try sampling the ADC. | ||

| + | ** updated tcl file, but still need to rely on project file as well as qsf file. | ||

| + | ** changed default level of adc_sclk to '1' | ||

| + | ** dac_clr_n was changed from an output to an input. | ||

| + | ** added 'locked' interface to rc_pll_stratix_iii | ||

| + | ** renamed the adc_pll clock signals to more explanitory names | ||

| + | ** added the FPGA_DEVICE_FAMILY generic to the dispatch interace for synthesis of the dc_fifo in lvds_rx | ||

| + | ** uncommented DDR interface to force the syntesizer to use correct left and right PLLs (in conjunction with ADC and DDR PLLs) | ||

| + | ** added test signals to test_status to see clocks on the scope. | ||

| + | == Revision 5.0.2 (buggy) == | ||

* '''Filename:''' | * '''Filename:''' | ||

** rc_v05000002_test00_tagged.sof | ** rc_v05000002_test00_tagged.sof | ||

| Line 195: | Line 517: | ||

* '''FPGA Resource Usage''' (readout_card.fit.rpt): | * '''FPGA Resource Usage''' (readout_card.fit.rpt): | ||

; Total logic elements ; 26,186 / 41,250 ( 63 % ) ; | ; Total logic elements ; 26,186 / 41,250 ( 63 % ) ; | ||

| − | |||

| − | |||

; Total memory bits ; 1,405,440 / 3,423,744 ( 41 % ) ; | ; Total memory bits ; 1,405,440 / 3,423,744 ( 41 % ) ; | ||

| − | |||

| − | |||

| − | |||

* '''FPGA Timing Analysis''' (readout_card.tan.rpt): | * '''FPGA Timing Analysis''' (readout_card.tan.rpt): | ||

| Line 207: | Line 524: | ||

; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk3' ; 16.067 ns ; | ; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk3' ; 16.067 ns ; | ||

| − | == Revision 5.0.1 (Filter + Raw + Rectangle, 2 LVDS) == | + | == Revision 5.0.1 (buggy) (Filter + Raw + Rectangle, 2 LVDS) == |

* '''Filename:''' | * '''Filename:''' | ||

** rc_v05000001_26may2009.sof | ** rc_v05000001_26may2009.sof | ||

| Line 214: | Line 531: | ||

** Combines features in rev. 5.0.0 (2 LVDS Lines) and rev. 4.0.e (Filtered + Raw), with the NEW rectangle mode. | ** Combines features in rev. 5.0.0 (2 LVDS Lines) and rev. 4.0.e (Filtered + Raw), with the NEW rectangle mode. | ||

** IMPORTANT: Must be used in conjunction with firmware rev. 5.0.0+ of all other cards. | ** IMPORTANT: Must be used in conjunction with firmware rev. 5.0.0+ of all other cards. | ||

| − | |||

| − | |||

| − | |||

* '''Bugs:''' | * '''Bugs:''' | ||

| Line 226: | Line 540: | ||

* '''FPGA Resource Usage''' (readout_card.fit.rpt): | * '''FPGA Resource Usage''' (readout_card.fit.rpt): | ||

; Total logic elements ; 26,565 / 41,250 ( 64 % ) ; | ; Total logic elements ; 26,565 / 41,250 ( 64 % ) ; | ||

| − | |||

| − | |||

; Total memory bits ; 1,405,440 / 3,423,744 ( 41 % ) ; | ; Total memory bits ; 1,405,440 / 3,423,744 ( 41 % ) ; | ||

| − | |||

| − | |||

| − | |||

* '''FPGA Timing Analysis''' (readout_card.tan.rpt): | * '''FPGA Timing Analysis''' (readout_card.tan.rpt): | ||

| Line 257: | Line 566: | ||

* '''FPGA Resource Usage''' (readout_card.fit.rpt): | * '''FPGA Resource Usage''' (readout_card.fit.rpt): | ||

| − | |||

| − | |||

; Total logic elements ; 26,607 / 41,250 ( 65 % ) ; | ; Total logic elements ; 26,607 / 41,250 ( 65 % ) ; | ||

| − | |||

| − | |||

; Total memory bits ; 406,016 / 3,423,744 ( 12 % ) ; | ; Total memory bits ; 406,016 / 3,423,744 ( 12 % ) ; | ||

| − | |||

| − | |||

| − | |||

* '''FPGA Timing Analysis''' (readout_card.tan.rpt): | * '''FPGA Timing Analysis''' (readout_card.tan.rpt): | ||

| Line 271: | Line 573: | ||

; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk2' ; 3.892 ns ; | ; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk2' ; 3.892 ns ; | ||

; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk3' ; 16.987 ns ; | ; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk3' ; 16.987 ns ; | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

= To-Do List = | = To-Do List = | ||

| − | * | + | * the starting point for the servo is currently zero and it would be nice to have it programmable. |

= RC Synthesis Notes = | = RC Synthesis Notes = | ||

| − | # Quartus.ini file had to exist in synth directory up to revision 4.0.a due to a bug that started in Quartus 6.1 and would synthesize away arbitrary parts of readout card. We contacted Altera at the time and they provided us the ini file | + | # The following note applies when using Quartus versions earlier than Q7: Quartus.ini file had to exist in synth directory up to revision 4.0.a due to a bug that started in Quartus 6.1 and would synthesize away arbitrary parts of readout card. We contacted Altera at the time and they provided us the ini file. |

# Timing: There is no "lock region" defined for readout card. Timing on readout card is tight and since version 3 or so any new feature would initially fail timing till some synthesis options were tweaked. One path that remains to be consistently marginal is from addr_gen counter (i.e. tga_o counter) in dispatch_wishbone.vhd to wishbone slaves particularly misc_banks_admin.vhd. Modules that are rewritten to address timing concerns are fsfb_corr, all_cards, misc_banks_admin, and finally instantiating an lpm counter instead of a counter from components library. Surprisingly, the lpm counter reduced 87 failures to 37, although looking at the technology map viewer, it seemed that they were both synthesized the same. | # Timing: There is no "lock region" defined for readout card. Timing on readout card is tight and since version 3 or so any new feature would initially fail timing till some synthesis options were tweaked. One path that remains to be consistently marginal is from addr_gen counter (i.e. tga_o counter) in dispatch_wishbone.vhd to wishbone slaves particularly misc_banks_admin.vhd. Modules that are rewritten to address timing concerns are fsfb_corr, all_cards, misc_banks_admin, and finally instantiating an lpm counter instead of a counter from components library. Surprisingly, the lpm counter reduced 87 failures to 37, although looking at the technology map viewer, it seemed that they were both synthesized the same. | ||

# Compile time: This was at some point 4.5 hours, after going to dual core PC, this was reduced to 35 minutes. After extending pid gains to 12b and fixing offset/sa_bias update code, the compile time increased to 1.5hr again with utilization up to ~70%. | # Compile time: This was at some point 4.5 hours, after going to dual core PC, this was reduced to 35 minutes. After extending pid gains to 12b and fixing offset/sa_bias update code, the compile time increased to 1.5hr again with utilization up to ~70%. | ||

| Line 599: | Line 585: | ||

lpm_file => "C:/scuba2_repository/cards/readout_card/fsfb_calc/source/rtl/ram_40x64.hex", and | lpm_file => "C:/scuba2_repository/cards/readout_card/fsfb_calc/source/rtl/ram_40x64.hex", and | ||

lpm_file : STRING; | lpm_file : STRING; | ||

| − | + | #Starting Q10.0 use TimeQuest timing analyzer as oppose to the classic one. The classic one is being phased out by Altera. In order to use TimeQuest, you need to have an sdc file present in your project directory. | |

| − | -- | + | * [[Pre-v5 firmware#Readout Card|Pre-v5 firmware]] |

| − | [ | + | [[Category:Readout Card Firmware| ]] |

Latest revision as of 11:32, 11 October 2022

An overview of the firmware implemented in Readout card is described here: [PDF]

- Synthesis Reminders (for firmware developers)

- Remember that readout_card/fsfb_clac/source/rtl/ram_40x64.vhd must be initialized with the ram_40x64.hex file in the same directory.

Contents

- 1 Revision 6.0.3

- 2 Revision 6.0.2 (TEST!)

- 3 Revision 5.2.2 (TEST!)

- 4 Revision 5.2.1 (recommended!)

- 5 Revision 5.2.0

- 6 Revision 5.1.d

- 7 Revision 5.1.b (Stable Rev.B Cards)

- 8 Revision 5.1.a (Stable)

- 9 Revision 5.1.6 (Stable)

- 10 Revision 5.1.2 (Stable)

- 11 Revision 5.0.f (Stable)

- 12 Revision 5.0.7 (type-2 filter)

- 13 Revision 5.0.4 (Stable)

- 14 Revision 5.0.3

- 15 To-Do List

- 16 RC Synthesis Notes

Revision 6.0.3

- Filename:

- Features:

- 6.0.2 was built based on a version that had an unsuccessful attempt to fix the filter dynamic-range issue. This version reverts back to 5.2.1 for fsfb_calc implementation.

- bugs

Revision 6.0.2 (TEST!)

- Features

- built based on 5.2.2

- added support of upper 32 word needs an additional wait cycle for ack_read

- delay wishbone readback by one clock cycle for reading back flx_quanta and adc_offset,

- there seem to be a filter gain of factor of 2 added

- bugs

Revision 5.2.2 (TEST!)

- Filename:

- bugfix or enhancement?

- fixes a dynamic-range issue with the filter by applying a 20-bit window to the output of stage 1 filter (with lsb being configurable) before passing it on the next stage.

- bugs

Revision 5.2.1 (recommended!)

- Filename:

- rc_stratixIII_v05020001_05jun2014.sof

- bugfix

- servo_rst_col# now works for all columns! (bug reported in 5.2.0)

- bugs

Revision 5.2.0

- Filename:

- rc_stratixIII_v05020000_28may2013.sof

- Features:

- added the ability to reset the flux-loop servo on per-detector basis by adding servo_rst_arm and servo_rst_col# parameters. This will reset the integral_term, the integral_clamp, anf flux-jump counter.

- bug:

- servo_rst_col# works for col 0 and 1, but not for col2 to 7! This is fixed in 5.2.1

- per-pixel servo reset doesn't also reset the filter

- resetting any pixel with per-pixel reset also resets all the pixels in the last row (as specified by num_rows, ignoring row_order)

Revision 5.1.d

- Filename:

- rc_stratixIII_v0501000d_30oct2012.sof

- Features:

- flux-jump routine is revamped to minimize the additional delay for applying sq1fb when flux-jump is enabled. In this version sq1fb DAC is refreshed at clock cycle 10 of each row visit when flux-jump is enabled and at clock cycle 7 when flux-jump is disabled.

- extended dynamic range of the filter by increasing the width of filter-delay terms from 29 to 32 bits

- lower power consumption (maybe?)

- Details

- DDR2 module not instantiated (chips not installed) and on-chip termination resistors not in effect which can potentially save power.

Revision 5.1.c (Test)

- Filename:

- rc_stratixIII_v0501000c_31aug2012.sof

- Features:

- extended dynamic range of the filter by increasing the width of filter-delay terms from 29 to 32 bits

- based on 5.1.a

- lower power consumption (maybe?)

- data_mode=4 reports fb(29 downto 12) instead of fb(31) & fb(28 downto 12)! no sticky bit.

- Details

- DDR2 module not instantiated (chips not installed) and on-chip termination resistors not in effect which can potentially save power.

Revision 5.1.b (Stable Rev.B Cards)

- Filename:

- rc_v0501000b_23mar2012.sof (Rev. B cards)

- Features:

- based on 5.1.8 (used Q11SP1)

- added intergral_term fix from 5.1.9

- Details

- qterm (or filtered-p) implementation is not included, because the design doesn't fit on the FPGA on Rev. B cards anymore.

Revision 5.1.a (Stable)

- Filename:

- rc_stratix3_v0501000a_24jan2012.sof (Rev. E cards)

- Features:

- based on 5.1.9 (used Q10SP1)

- pterm_decay_bits (par_id = 0x64) is now programmable and is initially set to 0 to have pure p-term and be compatible with older firmware. (p-term implemented as q(n) = er(n) + b*q(n-1) where b=(1-1/2^k)with k=pterm_decay_bits)

- see bugfix in 5.1.9

Revision 5.1.9 (test)

- Filename:

- rc_stratix3_v05010009_23jan2012.sof (for Rev. E cards)

- Features:

- based on 5.1.8 (used Q10SP1)

- first implementation of decayed-p-term in sq1fb calculation. The p-term is now implemented as q(n) = er(n) + b*q(n-1) where b=(1-1/2^k) and k=3 hardcoded.

- added pterm_decay_bits (par_id=0x64) as a register set to 3, but not tied to k in pterm calculation yet.

- Bugfix:

- This version fixes the bug introduced starting 5.0.e, the integral-term used to calculate sq1fb was calculated based on coadded value of (sample_num-1) samples and then the integral term stored for next round included sample_num-2. This is almost like having a p-term..

Revision 5.1.8 (s1fb_dly=7)

- Filename:

- rc_stratix3_v05010008_11jan2012.sof (for Rev. E cards)

- Features:

- based on 5.1.7 (used Q10SP1)

- reverts back to applying S1fb after 7 clock cycles when flux-jump is off, and after 18 clock cycles when flux-jump is on.

Revision 5.1.7 (rectangle-mode bugfix)

- Filename:

- rc_stratix3_v05010007_17nov2011.sof (for Rev. E cards)

- Features:

- based on 5.1.6 (used Q10SP1)

- Bugfix:

- In all RC firmware prior to 5.1.7, the read pointer in the rectangle-mode data was being refreshed at ARZ even if it was in the middle of a long readout (large frame readout). This resulted in seeing duplicate data in high-data-rate rectangle-mode readout only when the following condition was _NOT_ true: (230 + 2*cc num_rows_reported*cc num_cols_reported) < (num_rows*row_len). This is fixed in 5.1.7.

Revision 5.1.6 (Stable)

- Filename:

- rc_stratix3_v05010006_27oct2011.sof (for Rev. E cards)

- Features:

- based on 5.1.5 (used Q10SP1)

- coadd window and feedback-calculation blocks are adjusted for ADC latency of readout card Rev. E

- Bugfix:

- sample_dly + sample_num = row_len should work now.

Revision 5.1.5 (test)

- Filename:

- rc_stratix3_v05010005_15sep2011.sof (for Rev. E cards)

- Features:

- based on 5.1.2

- reverts back to applying SQ1FB after 18 clock cycles whether flux-jumping is on or off

- Bugfix:

- All stratixiii firmware revisions prior to this version adjusted the co-add window for an ADC latency of 4 instead of 11. (Rev. E RC has serial ADC installed with 11 clock cycle latency.) The coadd window is now adjusted properly.

- Bug:

- The last row samples can not be used in servo_mode=3. For proper operation: sample_dly + sample_num needs to be < row_len - 7 (I think). Although, the coadd window was adjusted in this version, but the calculation block latches data before coadd is done (coadd_done_o signal).

Revision 5.1.4 (Scuba2)

- Filename:

- rc_v05010004_01jun2011.sof (for Rev. B cards)

- Features:

- based on 5.1.3

- sq1_fb applied after 7 clock cycles when flux-jump off, and after 18 when flux-jump is on.

- bugfix:

- fixed bug with fsfb_corr when reverting back to applying sq1fb after 7 clk cycles when fj is off

Revision 5.1.3 (Scuba2)

- Filename:

- rc_v05010003_01jun2011.sof (for Rev. B cards)

- Features:

- based on 5.1.2

- reverts back to applying SQ1FB after 7 clock cyclces when flux-jumping is off, and after 18 clock cycles when flux-jumping is on.

- k1 of filter params is now limited to k1<8. After generating coeffs for many filters, it is certain that this range is more than what we ever need.

Revision 5.1.2 (Stable)

- Filename:

- rc_stratix3_v05010002_18jan2011.sof (for Rev. E cards)

- rc_stratix3_v05010002_18jan2011.jic (for Rev. E cards)

- rc_v05010002_03feb2011.sof (for Rev. B cards)

- rc_v05010002_03feb2011.pof (for Rev. B cards)

- Features:

- based on 5.1.1 with k1 and k2 (filter params) limited to k1<16 and k2<32 in order to resolve the timing when compiling for smaller Stratix FPGA on RC Rev. B.

- Bug fix:

- the 2-rows-off filtered data readout introduced with configurable filter in rev. 5.1.0 and 5.1.1 is fixed now.

- Bugs:

- none so far.

- FPGA Resource Usage (readout_card.fit.rpt, rev. B)

; Total logic elements ; 33,285 / 41,250 ( 81 % ) ; ; Total pins ; 358 / 616 ( 58 % ) ; ; Total memory bits ; 1,405,440 / 3,423,744 ( 41 % ) ;

- FPGA Timing Analysis (readout_card.tan.rpt, rev. B)

; Fast Model Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk2' ; 6.591 ns ; Fast Model Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk0' ; 7.206 ns ; Fast Model Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk3' ; 18.299 ns

Revision 5.1.1 (test only)

- Filename:

- rc_v05010001_01dec2010.sof (for Rev. B cards)

- Features:

- based on 5.1.0, but k1 and k2 (filter params) are now limited to k1<16 and k2<32 in order to resolve the timing failures of compiling 5.1.0 for smaller Stratix FPGA on RC Rev. B.

- Bugs:

- filter mode data is off by 2 rows.

Revision 5.1.0 (test only)

- Filename:

- rc_stratix3_v05010000_01nov2010.sof (for Rev. E cards)

- rc_v05010000_01nov2010.sof (for Rev. B cards) has timing failures do not use!!!

- Features:

- added configurable filter parameters specified by fltr_coeff, default is the fcutoff/fsampl=122Hz/15kHz. see Digital 4-pole Butterworth Low-pass filter .

- fltr_type is set to 255 to indicate configurable filter parameters.

- Details

- It is built on Quartus10.1.

- tcl files had to be updated as cmp syntax is not supported in Q10 anymore.

- Rev. E cards now can be identified by reading back pcb_rev as part of card_type, therefore both stratix I and III sof/pof/jic are generated from the same source.

- Bugs:

- rc_v05010000_01nov2010.sof has timing failures that were overlooked, do not use this firmware for Rev.B cards.

- filter mode data is off by 2 rows.

- FPGA Resource Usage and Timing Report (readout_card.fit.rpt and readout_card.tan.rpt): logic usage is upto 85% from 66% in 5.0.d/e/f

Revision 5.0.f (Stable)

- Filename:

- rc_v0500000f_22oct2010.sof (for Rev. B cards)

- rc_stratix3_v0500000f_22oct2010.sof (for Rev. E cards)

- Features:

- Bugfix: integral clamp should work now. only positive integral_clamp values are valid!

- Details::

- SQ1FB is applied 18 clock cycles after start of a row visit (SQ1_Bias being applied) regardless of flux-jump being enabled or not. In pre-5.0.b firmware SQ1FB was being applied after 7 clock cycles when flux-jump was disabled and after 18 clock cycles when flux-jump was enabled.

- available for both Rev. E and Rev. B cards, the upper byte of card_type parameter now reports the pcb revision.

- development note: It is built on Quartus10.1.

- Bugs:

- none yet!

- FPGA Resource Usage (readout_card.fit.rpt):

; Total logic elements ; 27,377 / 41,250 ( 66 % ) ; ; Total pins ; 358 / 616 ( 58 % ) ; ; Total memory bits ; 1,405,440 / 3,423,744 ( 41 % ) ;

- FPGA Timing Analysis (readout_card.tan.rpt):

; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk0' ; 2.652 ns ; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk2' ; 3.385 ns ; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk3' ; 16.860 ns

Revision 5.0.e (test only)

- Filename:

- rc_v0500000e_06oct2010.sof

- Details:

- an unsuccessful attempt to fix integral_clamp, but changed the functionality so that it clamps at the value, but it doesn't hold the clamp. i.e., if the calculated sq1fb becomes less than the specified clamp value, the sq1fb is not clamped anymore. This is not a desired functionality!

Revision 5.0.d (test only)

- Filename:

- rc_v0500000d_04aug2010.sof

- Features:

- Bugfix: To fix the bug associated with negative flux-jumps, reverted to signed multiplier and hence, incremented the width of the flux-quanta multiplier input by 1.

- Details::

- SQ1FB is applied 18 clock cycles after start of a row visit (SQ1_Bias being applied) regardless of flux-jump being enabled or not. In pre-5.0.b firmware SQ1FB was being applied after 7 clock cycles when flux-jump was disabled and after 18 clock cycles when flux-jump was enabled.

- Bugs:

- integral_clamp is broken. To test the clamping, a servo-locked ramp was initiated on the sq1fb and then flux-jumping was turned on and observed by attaching a scope to the SQ1FB output. With integral_clamp=80000000, flux_quanta=8000, gaini=1, flux-jump enabled, we see scope snapshot used slow_fb_ramp.py script for testing.

- FPGA Resource Usage and Timing Report (readout_card.fit.rpt and readout_card.tan.rpt): no change compared to 5.0.a/b/c

Revision 5.0.c (test only)

- Filename:

- rc_v0500000c_16jun2010.sof

- Features:

- Based on rev. 5.0.b

- Re-introduced flux-jump counter clamping to maintain continuity in behavior from past versions of firmware in the field.

- Important: SQ1FB is applied 18 clock cycles after start of a row visit (SQ1_Bias being applied) regardless of flux-jump being enabled or not. In pre-5.0.b firmware SQ1FB was being applied after 7 clock cycles when flux-jump was disabled and after 18 clock cycles when flux-jump was enabled.

- Details:

- Bugs:

- flux-jump is broken. flux-jumping block misbehaves at the first jump in the negative range.

- FPGA Resource Usage (readout_card.fit.rpt):

; Total logic elements ; 26,800 / 41,250 ( 65 % ) ; ; Total pins ; 358 / 616 ( 58 % ) ; ; Total virtual pins ; 0 ; ; Total memory bits ; 1,405,440 / 3,423,744 ( 41 % ) ; ; DSP block 9-bit elements ; 76 / 112 ( 68 % ) ; ; Total PLLs ; 1 / 6 ( 17 % ) ; ; Total DLLs ; 0 / 2 ( 0 % ) ;

- FPGA Timing Analysis (readout_card.tan.rpt):

; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk0' ; 1.964 ns ; ; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk2' ; 4.382 ns ; ; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk3' ; 15.924 ns ;

Revision 5.0.b (test only)

- Filename:

- rc_v0500000b_03jun2010.sof

- Features:

- Based on rev. 5.0.a

- A bug that caused jumps in first-stage feedback, and detected as spikes in the raw data of pixels that were in servo_mode=0,1,2 was fixed. The jumps in FSFB were due to flux-jumping being enabled on live pixels with non-zero flx_quanta, and being disabled on the fly on dead pixels with flx_quanta=0. Flux-jumping is now disabled on a column-by-column basis if a column is in servo_mode = 0,1,2.

- Ineffective clamping was removed from the flux-jumping block (as per 5.0.9), as it is now replaced by the clamping that was perfected in rev. 5.0.10

- A sticky bit that only affected servo_mode=0,1,2 was also removed from the flux-jumping block.

- flx_lp_init commands now also clear the flux-jumping block as well.

- The 11-clock-cycle delay (in applying SQ1_FB) that in previous firmware only occurred when flux-jumping was enabled, now (in this version) is in effect all the time. Due to the bug-fix above, flux-jumping can be disabled on a column-by-column basis by setting servo_mode=0,1,2 when en_fb_jump=1. Before the change, this meant that constant values could be applied with or without the 11-cycle delay if en_fb_jump=1 or 0. To make the delay consistent, it is now always 11 cycles. As background, the flux-jumping block is pipelined, meaning that it does calculations for all 8 channels serially. The serialization is because of DSP-block limitations in the Readout Card FPGA that prevent us from doing all 8 channels in parallel. The reason that it takes 11 cycles to complete the flux-jumping calculations is because the values are computed for the eight channels in three ALU stages: 8 + 3 = 11 cycles. Adding 11 cycles to the 7 cycles of latency from other stages in the system results in: 11 + 7 = 18 cycles of latency from the start of a row dwell period before the first-stage feedback is applied. In rc_v5.0.c, I enforce the 18-cycle delay even when flux-jumping is not enabled to maintain uniformity across all eight channels, because flux-jumping is enabled/disabled on a per-channel basis. In other words, if I hadn't enforced the 18-cycle delay, some channels could have their feedback applied after 7 cycles, while others could have it applied after 18 cycles. I wasn't a fan of this non-uniformity. I realize that 18 cycles is a long time. In fact, so is 7. In the last few months, we have been discussing how to reduce these times to 1 cycle, because every experiment out there wants to multiplex as fast as possible, and the 7/18-delay is a rate limiting step.

- The flux-jumping code was re-arranged in the flux-jumping block to reflect the flow of data through the pipeline and make it easier to understand.

- Details:

- Bugs:

- flux-jump does not work when jumping to negative values.

- FPGA Resource Usage (readout_card.fit.rpt):

; Total logic elements ; 26,745 / 41,250 ( 65 % ) ; ; Total pins ; 358 / 616 ( 58 % ) ; ; Total virtual pins ; 0 ; ; Total memory bits ; 1,405,440 / 3,423,744 ( 41 % ) ; ; DSP block 9-bit elements ; 76 / 112 ( 68 % ) ; ; Total PLLs ; 1 / 6 ( 17 % ) ; ; Total DLLs ; 0 / 2 ( 0 % ) ;

- FPGA Timing Analysis (readout_card.tan.rpt):

; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk0' ; 1.459 ns ; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk2' ; 3.895 ns ; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk3' ; 15.956 ns

Revision 5.0.a (test only)

- Filename:

- rc_v0500000a_12mar2010.sof

- Features:

- Based on the merger of rev. 5.0.8 and 5.0.9.

- integral_clamp command is added where a clamp value is set for the integral term and once the integral term hits that value, the integral-term is clamped to that value and p-term and d-term are clamped to zero. When integral_term=0 then no clamping is in effect, similar to previous releases of firmware.

- The low pass filter has 20-bit input and f_3dB/f_samp = 122Hz/15kHz .

- The flux-jump clamping that was removed in 5.0.9 is included once again here, as we decided this is safer for now.

- Details:

- "lock_dat_left" parameter that was removed in 5.0.9 is now implemented as "lock_dat_lsb"

- Bugs:

- flx_lp_init does not reinitialize the flux-jump block

- Synthesis Notes:

- The quartus.ini file was present in the synth directory during synthesis

- tag name: rc_v0500000a_12mar2009! years were mixed up!

- FPGA Resource Usage (readout_card.fit.rpt):

- FPGA Timing Analysis (readout_card.tan.rpt):

Revision 5.0.9 (buggy)

- Filename:

- rc_v05000009_13nov2009.sof

- Features:

- Based on rev. 5.0.4

- Removes a sticky bit in pid calculation result storage -- in fsfb_processor.

- Adds a command to clamp the growth of the I-term to prevent wrapping and track down the source of Caltech's FSFB jumps.

- Removed the unused lock_dat_left parameter. The ability to shift left was moved to the fsfb_corr block some time ago.

- Fixed a sign extension bug acting on the flux quanta, which limited the value to 8191. Changed the extension from signed to unsigned.

- Removed ineffective clamping in the flux-jump calculation block.

- IMPORTANT: Must be used in conjunction with firmware rev. 5.0.0+ of all other cards.

- Details:

- Bugs:

- integral_clamp read/write command does not work.

- Synthesis Notes:

- The quartus.ini file was present in the synth directory during synthesis

- FPGA Resource Usage (readout_card.fit.rpt):

; Total logic elements ; 27,960 / 41,250 ( 68 % ) ; ; Total memory bits ; 1,405,440 / 3,423,744 ( 41 % ) ;

- FPGA Timing Analysis (readout_card.tan.rpt):

; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk0' ; 1.825 ns ; ; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk2' ; 3.878 ns ; ; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk3' ; 14.397 ns ;

Revision 5.0.8 (UBC only)

- Filename:

- rc_v05000008_09oct2009.sof

- Features:

- Based on rev. 5.0.4

- type 1 low-pass filter: f3dB=122Hz for fsample=15kHz

- Filter-input-width changed from 18b to 20b with no sticky bits!

- removed sticky bits in internal arithmetic of the filter.

Revision 5.0.7 (type-2 filter)

- Filename:

- rc_v05000007_09oct2009.sof

- Features:

- Based on rev. 5.0.4

- type-2 low-pass-filter: f3dB=75Hz for fsample=30000.

- Filter-input-width changed from 18b to 20b with no sticky bits!

- inter-biquad-gain-scaling for the filter is 2^14

- filter results are scaled down by 2^3 in the output of the filter.

- removed sticky bits in internal arithmetics

- _correction_ disabled in fsfb_proc_pidz

- Details:

- quartus.ini file was not present in synth directory.

- Bugs:

- none to report

- FPGA Resource Usage (readout_card.fit.rpt):

- FPGA Timing Analysis (readout_card.tan.rpt):

Revision 5.0.6 (UBC only)

- Filename:

- rc_stratix3_v05000006_15sep2009.sof

- Features:

- Only Valid for Rev. C/D Cards

- Based on rev. 5.0.3

- tcl file updated for Rev. D and aligned with top-level and qsf (project file).

- flux loop commented, just to try sampling the ADC.

- compiled with Q9.1

Revision 5.0.5 (UBC only)

- Filename:

- rc_v05000005_04sep2009.sof

- Features:

- Based on rev. 5.0.2

- changed the low-pass-filter to f(3db)=75Hz for f(sample)=30000.

- Details:

- quartus.ini file was not present in synth directory.

- Bugs:

- negative inputs to the filter cause filter to have a non-flat pass-band region. may have to do with sign-handling...

- FPGA Resource Usage (readout_card.fit.rpt):

- FPGA Timing Analysis (readout_card.tan.rpt):

Revision 5.0.4 (Stable)

- Filename:

- rc_v05000004_28aug2009.sof

- Features:

- Based on rev. 5.0.2

- BUG Fix: handles 14-bit flux quanta (changed the multiplier to unsigned)

- BUG Fix: changed standard logic vector extension from signed to unsigned in flux-jumping slave.

- IMPORTANT: Must be used in conjunction with firmware rev. 5.0.0+ of all other cards.

- Details:

- Bugs:

- None so far.

- Synthesis Notes:

- The quartus.ini file was present in the synth directory during synthesis

- FPGA Resource Usage (readout_card.fit.rpt):

; Total logic elements ; 26,170 / 41,250 ( 63 % ) ; ; Total memory bits ; 1,405,440 / 3,423,744 ( 41 % ) ;

- FPGA Timing Analysis (readout_card.tan.rpt):

; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk0' ; 2.541 ns ; ; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk2' ; 3.612 ns ; ; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk3' ; 15.398 ns ;

Revision 5.0.3

- Filename:

- rc_stratix3_v05000003_21aug2009.sof

- Features:

- ONLY valid REV C/D RC Cards

- Based on rev. 5.0.2

- flux loop commented, just to try sampling the ADC.

- updated tcl file, but still need to rely on project file as well as qsf file.

- changed default level of adc_sclk to '1'

- dac_clr_n was changed from an output to an input.

- added 'locked' interface to rc_pll_stratix_iii

- renamed the adc_pll clock signals to more explanitory names

- added the FPGA_DEVICE_FAMILY generic to the dispatch interace for synthesis of the dc_fifo in lvds_rx

- uncommented DDR interface to force the syntesizer to use correct left and right PLLs (in conjunction with ADC and DDR PLLs)

- added test signals to test_status to see clocks on the scope.

Revision 5.0.2 (buggy)

- Filename:

- rc_v05000002_test00_tagged.sof

- Features:

- Based on rev. 5.0.1

- Fixed a bug in wbs_frame_data that stored data incorrectly if reporting 1 or 2 pixels only.

- IMPORTANT: Must be used in conjunction with firmware rev. 5.0.0+ of all other cards.

- Details:

- Bugs:

- None so far.

- Synthesis Notes:

- The quartus.ini file was present in the synth directory during synthesis.

- FPGA Resource Usage (readout_card.fit.rpt):

; Total logic elements ; 26,186 / 41,250 ( 63 % ) ; ; Total memory bits ; 1,405,440 / 3,423,744 ( 41 % ) ;

- FPGA Timing Analysis (readout_card.tan.rpt):

; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk0' ; 2.755 ns ; ; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk2' ; 3.979 ns ; ; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk3' ; 16.067 ns ;

Revision 5.0.1 (buggy) (Filter + Raw + Rectangle, 2 LVDS)

- Filename:

- rc_v05000001_26may2009.sof

- Features:

- Combines features in rev. 5.0.0 (2 LVDS Lines) and rev. 4.0.e (Filtered + Raw), with the NEW rectangle mode.

- IMPORTANT: Must be used in conjunction with firmware rev. 5.0.0+ of all other cards.

- Bugs:

- Has a bug in wbs_frame_data that stored data incorrectly if reporting 1 or 2 pixels only.

- Synthesis Notes:

- The quartus.ini file was present in the synth directory during synthesis.

- FPGA Resource Usage (readout_card.fit.rpt):

; Total logic elements ; 26,565 / 41,250 ( 64 % ) ; ; Total memory bits ; 1,405,440 / 3,423,744 ( 41 % ) ;

- FPGA Timing Analysis (readout_card.tan.rpt):

; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk0' ; 2.656 ns ; ; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk2' ; 3.861 ns ; ; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk3' ; 14.167 ns ;

Revision 5.0.0 (Filter Only, 2 LVDS)

- Filename:

- rc_v05000000_22dec2008.sof (tagged as sys_v05000000_22dec2008)

- Features:

- IMPORTANT: Must be used in conjunction with firmware v05000000+ of all other cards!!!

- Adds the ability to read out one column of data continuously from readout cards

- Adds data mode 11, which is an engineering mode. Data points are 32-bits, and bits [9..3]=row_index, [2..0]=column_index. This mode is useful for determining which pixels one is reading out in the array, in column mode for example.

- Bugs:

- None so far.

- Synthesis Notes:

- The quartus.ini file was not present in the synth directory during synthesis.

- FPGA Resource Usage (readout_card.fit.rpt):

; Total logic elements ; 26,607 / 41,250 ( 65 % ) ; ; Total memory bits ; 406,016 / 3,423,744 ( 12 % ) ;

- FPGA Timing Analysis (readout_card.tan.rpt):

; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk0' ; 2.558 ns ; ; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk2' ; 3.892 ns ; ; Clock Setup: 'rc_pll:i_rc_pll|altpll:altpll_component|_clk3' ; 16.987 ns ;

To-Do List

- the starting point for the servo is currently zero and it would be nice to have it programmable.

RC Synthesis Notes

- The following note applies when using Quartus versions earlier than Q7: Quartus.ini file had to exist in synth directory up to revision 4.0.a due to a bug that started in Quartus 6.1 and would synthesize away arbitrary parts of readout card. We contacted Altera at the time and they provided us the ini file.

- Timing: There is no "lock region" defined for readout card. Timing on readout card is tight and since version 3 or so any new feature would initially fail timing till some synthesis options were tweaked. One path that remains to be consistently marginal is from addr_gen counter (i.e. tga_o counter) in dispatch_wishbone.vhd to wishbone slaves particularly misc_banks_admin.vhd. Modules that are rewritten to address timing concerns are fsfb_corr, all_cards, misc_banks_admin, and finally instantiating an lpm counter instead of a counter from components library. Surprisingly, the lpm counter reduced 87 failures to 37, although looking at the technology map viewer, it seemed that they were both synthesized the same.

- Compile time: This was at some point 4.5 hours, after going to dual core PC, this was reduced to 35 minutes. After extending pid gains to 12b and fixing offset/sa_bias update code, the compile time increased to 1.5hr again with utilization up to ~70%.

- wbs_fb_storage, ram_8x64, pid_ram had to be regenerated using latest (Q7.2) MegaWizard to get rid of the bug associated with failure to read after power up until a reset was issued.

- During simulations, the initialization of RAM block with .hex files needs to be disabled. This is done by commenting out the following lines from the MegaWizard generated Megafunction files (remember to un-comment them before synthesizing the code):

lpm_file => "C:/scuba2_repository/cards/readout_card/fsfb_calc/source/rtl/ram_40x64.hex", and lpm_file : STRING;

- Starting Q10.0 use TimeQuest timing analyzer as oppose to the classic one. The classic one is being phased out by Altera. In order to use TimeQuest, you need to have an sdc file present in your project directory.