Difference between revisions of "MCE Timing Diagram"

From MCEWiki

| Line 41: | Line 41: | ||

|} | |} | ||

| − | Note that Bias Card DACs (MAX5443) latch on | + | Note that: |

| + | * Bias Card DACs (MAX5443) latch on low-to-high transition of CS (chip-select). Address Card DACs are clocked on the negative edge of the main clock. | ||

| − | + | * In Address Card section, both DAC_clk(0) and DAC_clk(32) are shown. This indicates that first, the previous row's DAC (32 in this case) is turned off and then the new DAC (0 in this case) is turned on. All Address-Card DACs are off for 2 clock cycles. | |

| − | The coadd window takes the 4 clock cycles of ADC latency into account, i.e., When the coadd window is asserted at clock cycle 40 in the diagram above, the samples are stored starting clock cycle 44. | + | * The coadd window takes the 4 clock cycles of ADC latency (for RC Rev. A) into account, i.e., When the coadd window is asserted at clock cycle 40 in the diagram above, the samples are stored starting clock cycle 44. |

| − | Bias Card DACs (MAX5443) have ~400ns settling delay (see FULL-SCALE STEP RESPONSE on page 6 [http://datasheets.maxim-ic.com/en/ds/MAX5441-MAX5444.pdf here], | + | ** Due to a bug up to firmware revision 5.1.4, the coadd window is always being adjusted for an ADC latency of 4 even if used with Rev. E cards which have an ADC latency of 11. This throws off the sampling window by 7 cycles. First recorded sample is from clock cycle: sample_dly-7. Or in another word, one has to make that correction when plugging in a number for sample_dly. This will be fixed in future firmware. |

| − | Address Card and Readout Card DACs (AD9744) have a settling delay of 11 ns, see Table 2, pg 4 o[http://www.analog.com/static/imported-files/data_sheets/AD9744.pdf here] | + | |

| + | * Bias Card DACs (MAX5443) have ~400ns settling delay (see FULL-SCALE STEP RESPONSE on page 6 [http://datasheets.maxim-ic.com/en/ds/MAX5441-MAX5444.pdf here], | ||

| + | |||

| + | * Address Card and Readout Card DACs (AD9744) have a settling delay of 11 ns, see Table 2, pg 4 o[http://www.analog.com/static/imported-files/data_sheets/AD9744.pdf here] | ||

| + | == Raw mode timing diagram == | ||

Revision as of 12:24, 13 September 2011

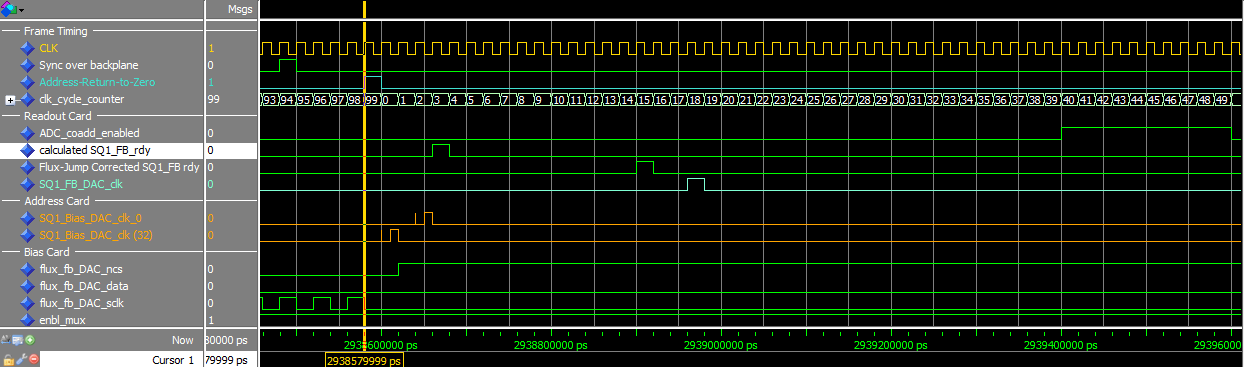

The following timing diagram is generated by simulating MCE firmware using ModelsimTM, therefore, it does not include the analog circuit delays (DAC delay, RC filters, settling time, etc) into account.

Parameters used for this simulation:

Parameters used for this simulation:

| row_len | 100 |

| num_rows | 33 |

| sample_dly | 40 |

| sample_num | 10 |

| servo_mode | 3 |

| Address Card enbl_mux | 1 |

| Bias Card enbl_mux | 1 |

| RC firmware rev. | 5.1.2 |

| BC firmware rev. | 5.0.5 |

| AC firmware rev. | 5.0.3 |

| CC firmware rev. | 5.0.7 |

Note that:

- Bias Card DACs (MAX5443) latch on low-to-high transition of CS (chip-select). Address Card DACs are clocked on the negative edge of the main clock.

- In Address Card section, both DAC_clk(0) and DAC_clk(32) are shown. This indicates that first, the previous row's DAC (32 in this case) is turned off and then the new DAC (0 in this case) is turned on. All Address-Card DACs are off for 2 clock cycles.

- The coadd window takes the 4 clock cycles of ADC latency (for RC Rev. A) into account, i.e., When the coadd window is asserted at clock cycle 40 in the diagram above, the samples are stored starting clock cycle 44.

- Due to a bug up to firmware revision 5.1.4, the coadd window is always being adjusted for an ADC latency of 4 even if used with Rev. E cards which have an ADC latency of 11. This throws off the sampling window by 7 cycles. First recorded sample is from clock cycle: sample_dly-7. Or in another word, one has to make that correction when plugging in a number for sample_dly. This will be fixed in future firmware.

- Bias Card DACs (MAX5443) have ~400ns settling delay (see FULL-SCALE STEP RESPONSE on page 6 here,

- Address Card and Readout Card DACs (AD9744) have a settling delay of 11 ns, see Table 2, pg 4 ohere