Difference between revisions of "Readout Card Preamp Chain"

| (52 intermediate revisions by 4 users not shown) | |||

| Line 1: | Line 1: | ||

| − | + | == Preamp Chain in Readout Card == | |

| + | The preamp chain consists of four stages of amplification which provide gain and act as a low pass filter. Six RC poles are included in the chain and act together to give a steep roll off which limits out-of-band noise. The exact pole locations and filter cut-off frequency depends upon the particular readout-card revision, but the basic topology is consistent across all revisions up to the latest revision (E). This topology consists of two initial low noise amplifier stages each with a single RC pole in their respective feedback loops (R12&C74 followed by R14&C75 in Rev B), followed by a third stage of gain which also includes another RC pole in its feedback loop (R16&C76 in Rev B), and finally a differential ADC driver which has symmetric RC poles on both the positive and negative outputs (R10&C73 and R24&C77 in Rev B). There is also a low-pass RC filter between the first and second stages (R20&C78 in Rev B) and third and fourth stages (R21&C79 in Rev B). | ||

| − | + | The plots shown here are generated by collecting [[Raw-mode readout | raw data]] sampled at 50 MHz, with the cold electronics replaced by test boards which short all of the instrument backplane lines with 50 ohm resistors. A summary of the results is in the table below. | |

| − | + | {| class="wikitable" | |

| − | + | |+ Preamp Bandwidth across Readout Card Revisions | |

| + | |- | ||

| + | ! Board Revision !! Noise (RMS) !! Bandwidth (f3dB)!! Attenuation at 500 kHz | ||

| + | |- | ||

| + | | [[Readout Card Preamp Chain#Rev_B9|B9 (shorted)]] | ||

| + | || 4.2 ADC units | ||

| + | || 5.7 MHz | ||

| + | || 0.1 dB | ||

| + | |- | ||

| + | | [[Readout Card Preamp Chain#Rev_B10|B10 (50 Ohm)]] | ||

| + | || 3.0 ADC units | ||

| + | || 1.27 MHz | ||

| + | || 0.6 dB | ||

| + | |- | ||

| + | | [[Readout Card Preamp Chain#Rev_E0|E0 (shorted)]] | ||

| + | || 3.2 ADC units | ||

| + | || 3.2 MHz | ||

| + | || 0.2 dB | ||

| + | |- | ||

| + | |} | ||

| − | |||

| − | |||

| − | + | == Rev B9 == | |

| + | [http://www.phas.ubc.ca/~mce/mcedocs/hardware/schematics/Readout%20Card%20RevD/RC_C582_101D0_Schematic.pdf RC Rev B9 Schematic (preamp chain on page 7)] | ||

| − | + | The gain distribution among different amplification stages in Revision B is: 4, 4, 6, 2, for a total gain of 192. The card uses a 16 bit ADC with a 2.2 V reference, leading to a LSB size of 134 uV. The 3dB cutoff frequency of the chain is about 6 MHz. The noise of the preamp chain is approximately 5.4 ADC units with a 50 ohm resistor at the MDM connector, or about 4.2 ADC units with the preamp shorted. | |

| − | + | Test results using a Revision B9 card with a 50 ohm resistance at the MDM connector are shown below. | |

| + | {|"wikitable" | ||

| + | |- | ||

| + | |[[Image: dB_spectra_1267481760_raw.png|400px|thumb]] | ||

| + | |- | ||

| + | |[[Image: timestream_1267481760_raw.png|400px|thumb]] | ||

| + | |- | ||

| + | [[Image: spectra_1267481760_raw.png|400px|thumb]] | ||

| + | |- | ||

| + | |} | ||

| − | + | == Rev B10 == | |

| + | The schematic for Rev B10 is identical to that of B9, excepting 3 capacitor value changes on each channel of the preamp. These capacitors were altered to reduce the cutoff frequency of the preamp chain in order to reduce out of band noise. The designed cutoff frequency was reduced from 6MHz to about 1.4 MHz, which predicts a reduction in total noise across the full band of the ADC of approximately Sqrt(1.4/6), or a little bit better than 50%. | ||

| − | + | The gain distribution of Revision B is: first stage 4, second stage 4, third stage 6, fourth stage 2, for a total gain of 192. The card uses a 16 bit ADC with a 2.2 V reference, leading to a LSB size of 134 uV. The measured noise was about 3.0 ADC units. The maximum signal frequency of interest (500 kHz) is attenuated by about 0.6 dB by the filter compared to DC gain. | |

| − | : | ||

| − | |||

| − | |||

| − | |||

| − | + | In order to achieve the lower cutoff frequency, capacitors C74, C75 and C76 were altered to 470pF, 470pF, and 68pF respectively. This shifts the pole locations: | |

| − | |||

| − | |||

| − | : | ||

| − | + | {| class="wikitable" | |

| − | + | |- | |

| + | ! pole!! Components!! Frequency (MHz)<br>Rev B10!! Frequency (MHz)<br>Rev B9 | ||

| + | |- | ||

| + | |pole 1 ||R12 & C74 || 3.4 MHz || 15.9 MHz | ||

| + | |- | ||

| + | |pole 2 ||R20 & C78 || 10.2 MHz ||(unchanged) | ||

| + | |- | ||

| + | |pole 3 ||R14 & C75 || 3.4 MHz || 15.9 MHz | ||

| + | |- | ||

| + | |pole 4 ||R21 & C79 || 10.2 MHz ||(unchanged) | ||

| + | |- | ||

| + | |pole 5 ||R16 & C76 || 2.3 MHz ||7.2 MHz | ||

| + | |- | ||

| + | |pole 6 ||R10 & C73, R24 & C77 || 7.2 MHz ||7.2 | ||

| + | |- | ||

| + | |} | ||

| − | The | + | The combination of these poles results in a total cutoff frequency (calculated via SPICE simulation using ideal opamps) of 1.44 MHz. The actual cutoff frequency is expected to be slightly lower than this due to the use of AD797 op amps in the first two stages, which have low roll off frequencies (estimated at between 10 and 20 MHz at a gain of 4) that contribute to further reduction of the overall cutoff frequency. The uncertainty in the resistors (1%) and capacitors (5%) result in a maximum variation of overall cutoff frequency between (calculated using SPICE simulation) 1.37 MHz and 1.53 MHz around the nominal value of 1.44 MHz. |

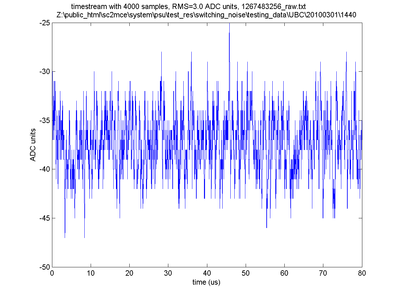

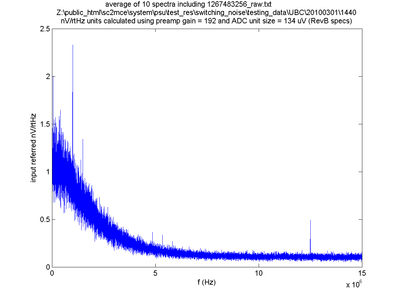

| − | + | Test results using a Revision B10 card are shown below. | |

| + | {|"wikitable" | ||

| + | |- | ||

| + | |[[Image: dB_spectra_1267483256_raw.png|400px|thumb]] | ||

| + | |- | ||

| + | |[[Image: timestream_1267483256_raw.png|400px|thumb]] | ||

| + | |- | ||

| + | |[[Image: spectra_1267483256_raw.png|400px|thumb]] | ||

| + | |- | ||

| + | |} | ||

| + | == Rev E0 == | ||

| + | [http://www.phas.ubc.ca/~mce/mcedocs/hardware/schematics/Readout%20Card%20RevE/RC_C582_101E0_Schematic.pdf RC Rev E0 Schematic (preamp chain on page 11)] | ||

| − | + | The Rev E0 preamp chain has several changes. The first and second stage op amps have been changed from the AD797 to the ADA4898-1. This change should provide improved flatness in frequency response, lower noise, and more predictable gain and bandwidth properties. The gain structure and pole frequencies have also changed in an effort to reduce the noise contribution of the preamp itself, aliased squid noise, and thermal noise of the cable impedance. By reducing the bandwidth to a minimum acceptable for the different cable impedances encountered in various experiments, the noise bandwidth is reduced. | |

| − | |||

| − | + | The new gain distribution between stages is: 6.13, 5.99, 5.52, 1 with an overall gain of 203. | |

| − | = | + | The new pole frequencies are: |

| − | + | {| class="wikitable" | |

| + | |- | ||

| + | ! pole!! Frequency (MHz) | ||

| + | |- | ||

| + | |pole 1|| 9.7 MHz | ||

| + | |- | ||

| + | |pole 2 || 15.2 MHz | ||

| + | |- | ||

| + | |pole 3|| 9.7 MHz | ||

| + | |- | ||

| + | |pole 4 || 15.2 MHz | ||

| + | |- | ||

| + | |pole 5 ||7.2 MHz | ||

| + | |- | ||

| + | |} | ||

| − | |||

| − | + | These poles, along with the roll off of the op amps resulting from internal compensation, yield an overall 3dB frequency for the preamp chain of approximately 3.2 MHz. It is important to remember that this is the cutoff frequency of the preamp chain alone, and does not include the filter board capacitors (150pF) or cable impedance, which interact to form a low frequency pole which can dominate the overall cutoff frequency. For example, a cable with impedance ~200ohms+100pF adds a pole near 3 MHz, which would reduce the overall bandwidth to about 2 MHz. | |

| − | + | The series resistor between the feedback network of the first stage op amp and the offset adjust DAC, R37, has also been changed. It has been reduced to 681 ohms to allow a greater offset to be trimmed out. This change has a minor effect on the gain due to the interaction between resistor R37 and R11, increasing the gain slightly. This has already been included in the gain calculation above, and accounts for the difference in gain between the first and second stage. | |

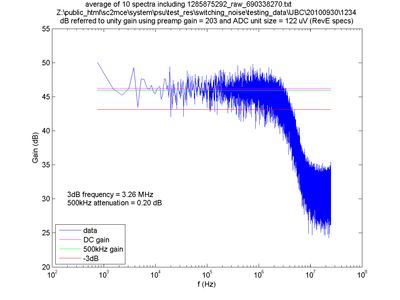

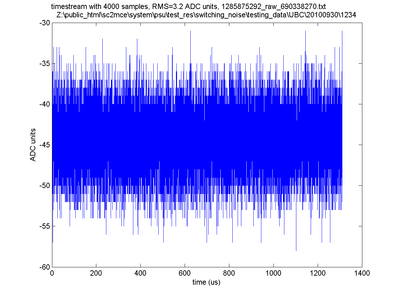

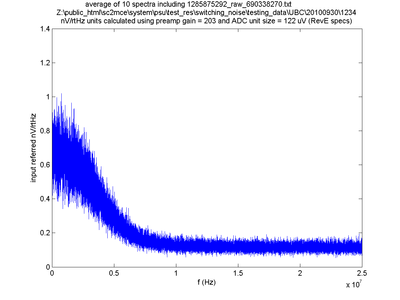

| − | + | Some typical test results of a Rev E0 card are shown below. | |

| − | + | {|"wikitable" | |

| + | |- | ||

| + | |[[Image: dB spectra 1285875292 raw 690338270.png|400px|thumb]] | ||

| + | |- | ||

| + | |[[Image: Timestream 1285875292 raw 690338270.png|400px|thumb]] | ||

| + | |- | ||

| + | |[[Image: Spectra 1285875292 raw 690338270.png|400px|thumb]] | ||

| + | |} | ||

| − | + | [[Category:Readout Card]] | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

Latest revision as of 15:26, 31 August 2016

Preamp Chain in Readout Card

The preamp chain consists of four stages of amplification which provide gain and act as a low pass filter. Six RC poles are included in the chain and act together to give a steep roll off which limits out-of-band noise. The exact pole locations and filter cut-off frequency depends upon the particular readout-card revision, but the basic topology is consistent across all revisions up to the latest revision (E). This topology consists of two initial low noise amplifier stages each with a single RC pole in their respective feedback loops (R12&C74 followed by R14&C75 in Rev B), followed by a third stage of gain which also includes another RC pole in its feedback loop (R16&C76 in Rev B), and finally a differential ADC driver which has symmetric RC poles on both the positive and negative outputs (R10&C73 and R24&C77 in Rev B). There is also a low-pass RC filter between the first and second stages (R20&C78 in Rev B) and third and fourth stages (R21&C79 in Rev B).

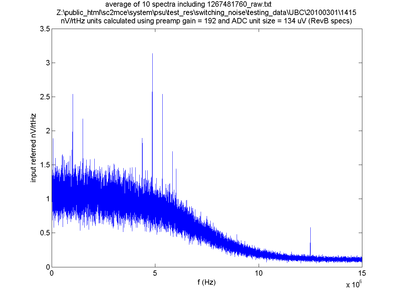

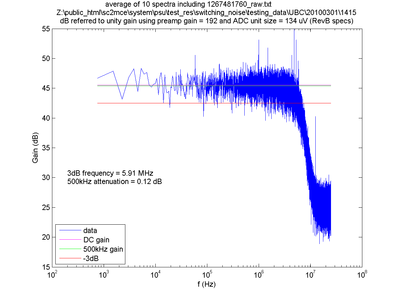

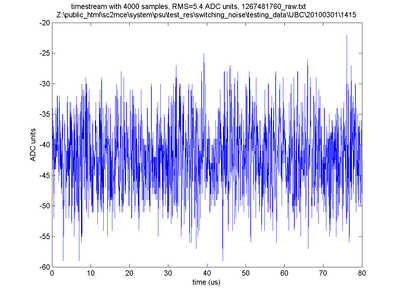

The plots shown here are generated by collecting raw data sampled at 50 MHz, with the cold electronics replaced by test boards which short all of the instrument backplane lines with 50 ohm resistors. A summary of the results is in the table below.

| Board Revision | Noise (RMS) | Bandwidth (f3dB) | Attenuation at 500 kHz |

|---|---|---|---|

| B9 (shorted) | 4.2 ADC units | 5.7 MHz | 0.1 dB |

| B10 (50 Ohm) | 3.0 ADC units | 1.27 MHz | 0.6 dB |

| E0 (shorted) | 3.2 ADC units | 3.2 MHz | 0.2 dB |

Rev B9

RC Rev B9 Schematic (preamp chain on page 7)

The gain distribution among different amplification stages in Revision B is: 4, 4, 6, 2, for a total gain of 192. The card uses a 16 bit ADC with a 2.2 V reference, leading to a LSB size of 134 uV. The 3dB cutoff frequency of the chain is about 6 MHz. The noise of the preamp chain is approximately 5.4 ADC units with a 50 ohm resistor at the MDM connector, or about 4.2 ADC units with the preamp shorted.

Test results using a Revision B9 card with a 50 ohm resistance at the MDM connector are shown below.

Rev B10

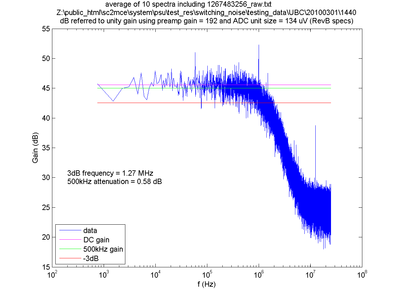

The schematic for Rev B10 is identical to that of B9, excepting 3 capacitor value changes on each channel of the preamp. These capacitors were altered to reduce the cutoff frequency of the preamp chain in order to reduce out of band noise. The designed cutoff frequency was reduced from 6MHz to about 1.4 MHz, which predicts a reduction in total noise across the full band of the ADC of approximately Sqrt(1.4/6), or a little bit better than 50%.

The gain distribution of Revision B is: first stage 4, second stage 4, third stage 6, fourth stage 2, for a total gain of 192. The card uses a 16 bit ADC with a 2.2 V reference, leading to a LSB size of 134 uV. The measured noise was about 3.0 ADC units. The maximum signal frequency of interest (500 kHz) is attenuated by about 0.6 dB by the filter compared to DC gain.

In order to achieve the lower cutoff frequency, capacitors C74, C75 and C76 were altered to 470pF, 470pF, and 68pF respectively. This shifts the pole locations:

| pole | Components | Frequency (MHz) Rev B10 |

Frequency (MHz) Rev B9 |

|---|---|---|---|

| pole 1 | R12 & C74 | 3.4 MHz | 15.9 MHz |

| pole 2 | R20 & C78 | 10.2 MHz | (unchanged) |

| pole 3 | R14 & C75 | 3.4 MHz | 15.9 MHz |

| pole 4 | R21 & C79 | 10.2 MHz | (unchanged) |

| pole 5 | R16 & C76 | 2.3 MHz | 7.2 MHz |

| pole 6 | R10 & C73, R24 & C77 | 7.2 MHz | 7.2 |

The combination of these poles results in a total cutoff frequency (calculated via SPICE simulation using ideal opamps) of 1.44 MHz. The actual cutoff frequency is expected to be slightly lower than this due to the use of AD797 op amps in the first two stages, which have low roll off frequencies (estimated at between 10 and 20 MHz at a gain of 4) that contribute to further reduction of the overall cutoff frequency. The uncertainty in the resistors (1%) and capacitors (5%) result in a maximum variation of overall cutoff frequency between (calculated using SPICE simulation) 1.37 MHz and 1.53 MHz around the nominal value of 1.44 MHz.

Test results using a Revision B10 card are shown below.

Rev E0

RC Rev E0 Schematic (preamp chain on page 11)

The Rev E0 preamp chain has several changes. The first and second stage op amps have been changed from the AD797 to the ADA4898-1. This change should provide improved flatness in frequency response, lower noise, and more predictable gain and bandwidth properties. The gain structure and pole frequencies have also changed in an effort to reduce the noise contribution of the preamp itself, aliased squid noise, and thermal noise of the cable impedance. By reducing the bandwidth to a minimum acceptable for the different cable impedances encountered in various experiments, the noise bandwidth is reduced.

The new gain distribution between stages is: 6.13, 5.99, 5.52, 1 with an overall gain of 203.

The new pole frequencies are:

| pole | Frequency (MHz) |

|---|---|

| pole 1 | 9.7 MHz |

| pole 2 | 15.2 MHz |

| pole 3 | 9.7 MHz |

| pole 4 | 15.2 MHz |

| pole 5 | 7.2 MHz |

These poles, along with the roll off of the op amps resulting from internal compensation, yield an overall 3dB frequency for the preamp chain of approximately 3.2 MHz. It is important to remember that this is the cutoff frequency of the preamp chain alone, and does not include the filter board capacitors (150pF) or cable impedance, which interact to form a low frequency pole which can dominate the overall cutoff frequency. For example, a cable with impedance ~200ohms+100pF adds a pole near 3 MHz, which would reduce the overall bandwidth to about 2 MHz.

The series resistor between the feedback network of the first stage op amp and the offset adjust DAC, R37, has also been changed. It has been reduced to 681 ohms to allow a greater offset to be trimmed out. This change has a minor effect on the gain due to the interaction between resistor R37 and R11, increasing the gain slightly. This has already been included in the gain calculation above, and accounts for the difference in gain between the first and second stage.

Some typical test results of a Rev E0 card are shown below.